SPI概念

SPI,serial peripheral interface,串行外设设备接口。

是motorola首先在其MC68HCXX系列处理器上定义的。

SPI接口主要引用与EEPEOM,FLASH,各种传感器,AD转换器等。

SPI,是一种高速的,全双工的,同步的穿行通信总线。

物理层

1个SPI设备一般有4条线

SCK:时钟信号线,用于通讯数据同步。

它由通讯主机(MCU)产生,决定了通讯的速率。

不同的设备支持的最高时钟频率不一样,如STM32的SPI时钟频率最大为fpclk/2(连接外设总线的1/2)。

两个设备之间通讯时,通讯速率受限于低速设备。

MOSI:主设备输出/从设备输入引脚。

主机的数据从这条信号线输出,从机有这条信号线读入主机发送的数据,这条线上的数据方向为主机到从机。

MISO:主设备输入/从设备输出引脚。

主机从这条信号线读入数据,从记得数据由这条信号线输出到主机。

在这条线上数据的方向为从机到主机。

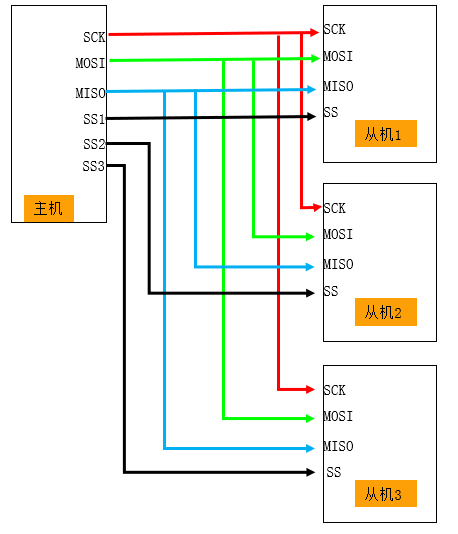

SS:片选线或者使能线。有时候也称NSS或CS。

叫NSS是因为SS位一般置0为开始传输数据的标志,CS(chip selection)。

SPI通信时各个设备时没有地址的。

主机和哪个从机通讯,就把谁的SS置为低电平。

如果要主机连接多条从设备就需要多条片选线。

主从设备连接示例

只能主从设备之间进行通信,从与从之间无法进行通信。

协议层

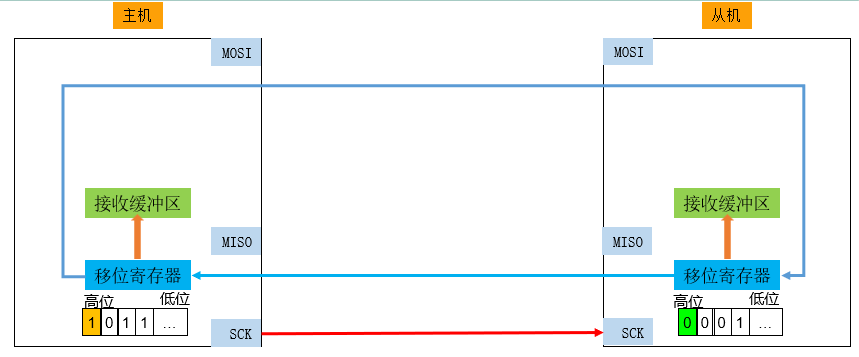

主机和从机之间的数据交换

以为寄存器临时存储要交换的数据(来自于发送缓冲区)。

接受缓冲区存储最终得到的值。

来一个时钟上升沿信号,主机和从机分别把自己的高位的值左移出来(一般高位先行)。

来一个时钟下降沿信号,主机和从机分别读入数据,存储到移位寄存器的低位。

经过8次同样的操作,就完成了一个字节的交换。

最后从接收缓冲区就可以读出数据了。

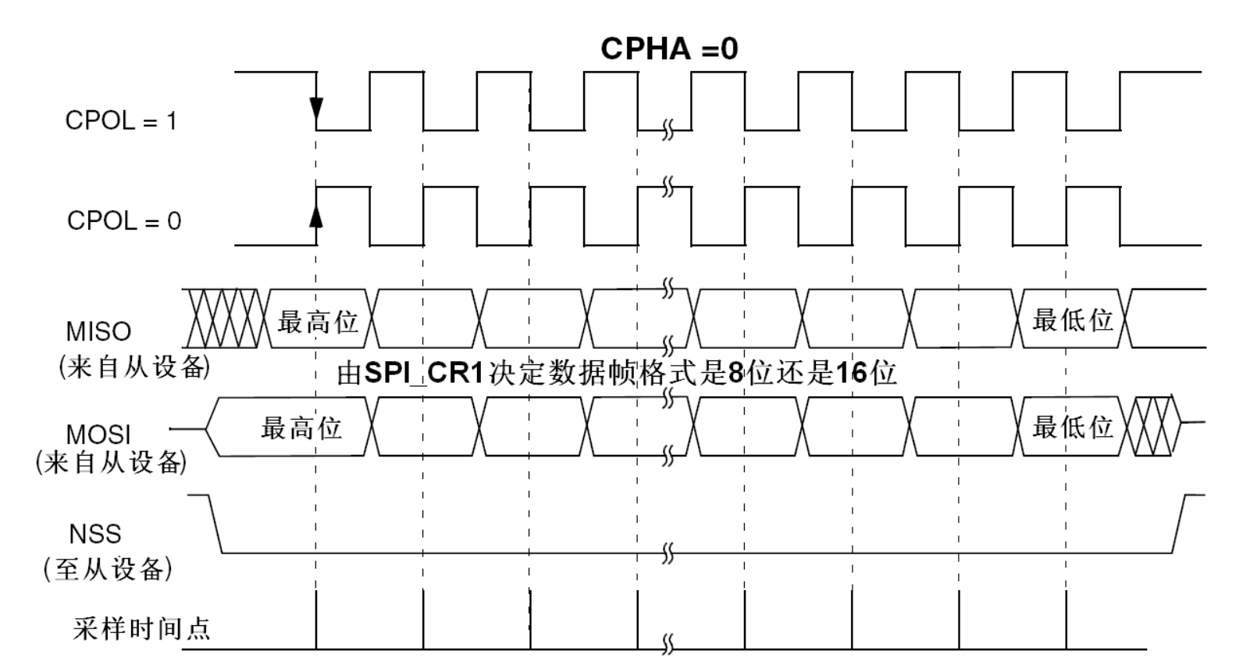

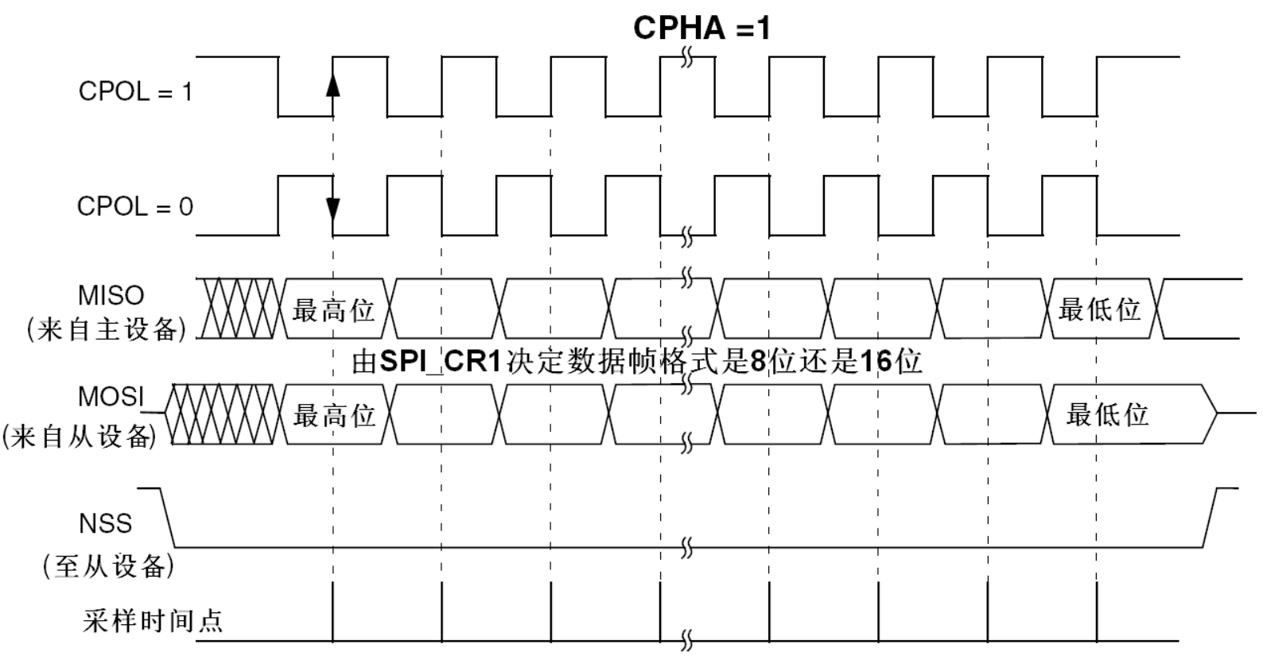

时钟的极性和相位

前面描述的是简单化了的数据交换过程,其实什么时候读数据(数据采样),和设置的时钟极性和相位有关。

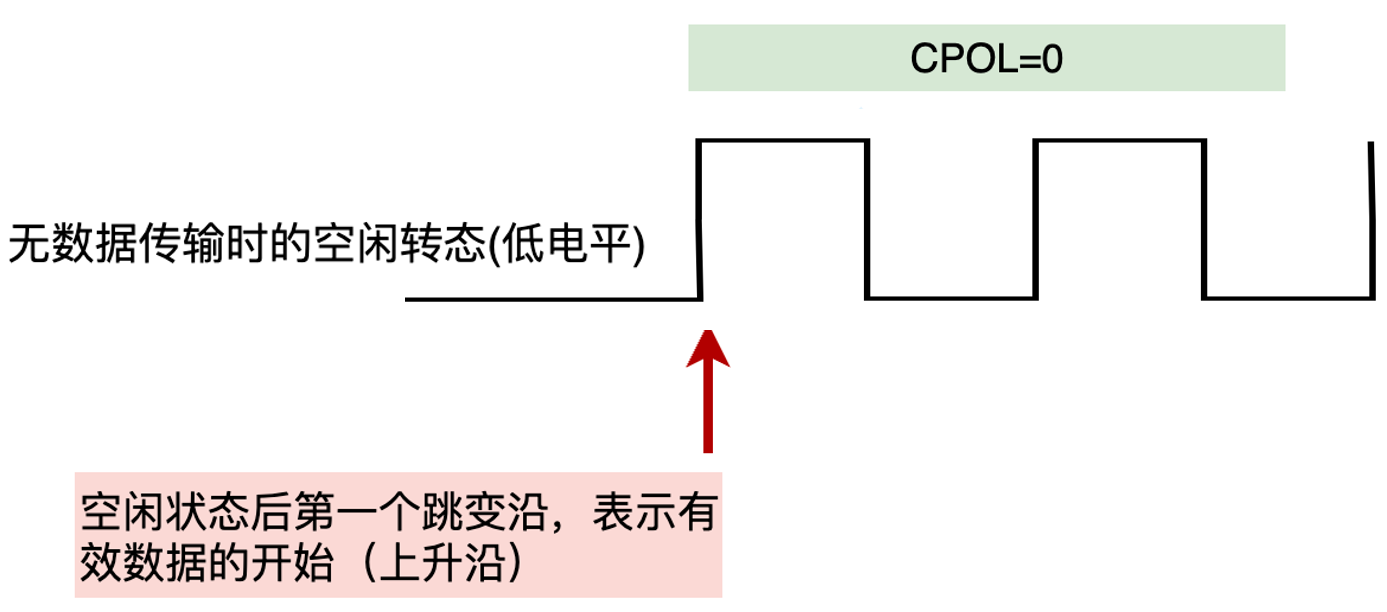

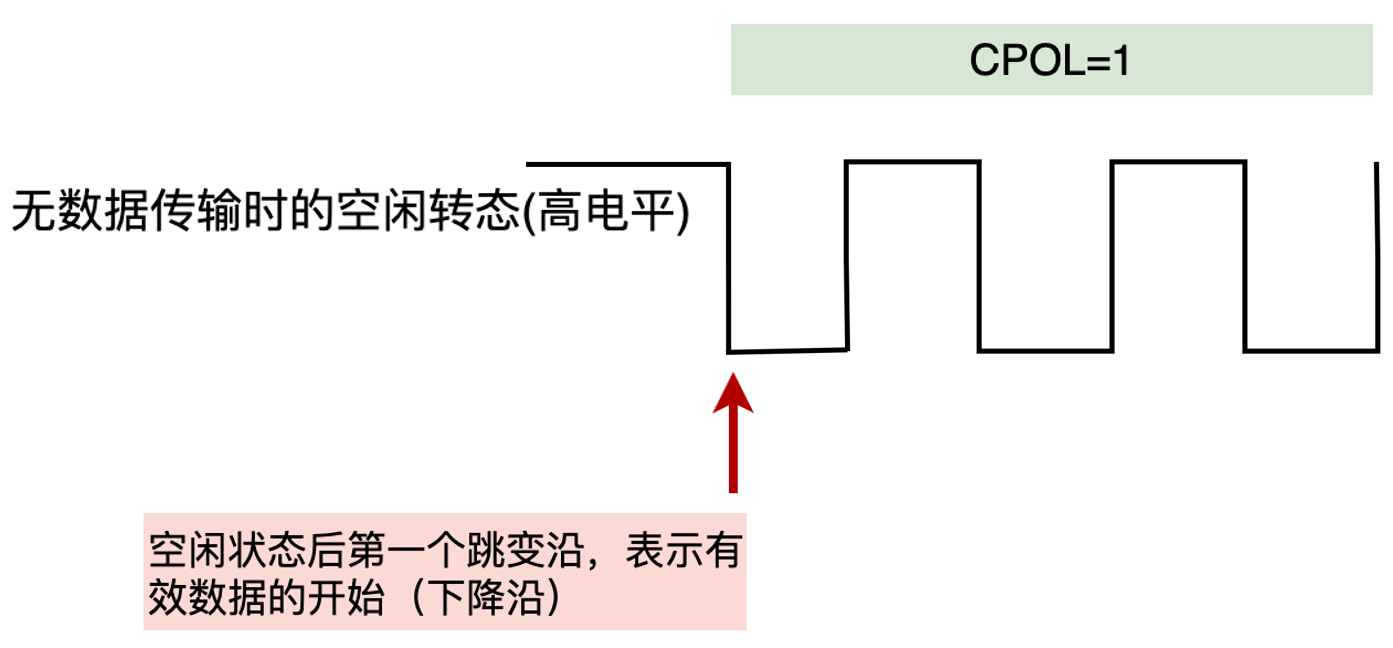

时钟的极性

CPOL:clock polarity

通信的整个过程分为空闲时刻可和通信时刻。

空闲状态SCK是低电平,CPOL=0。

空闲状态SCK是高电平,CPOL=1。

时钟的相位

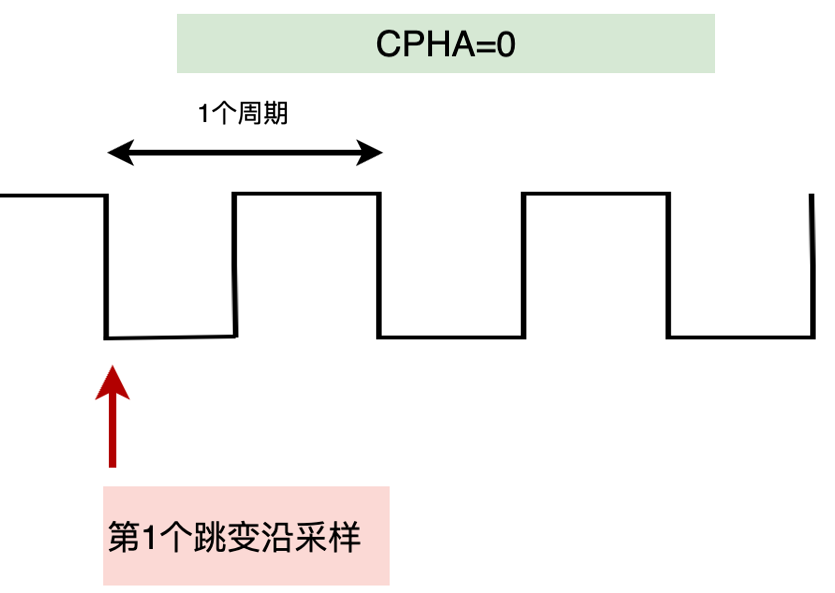

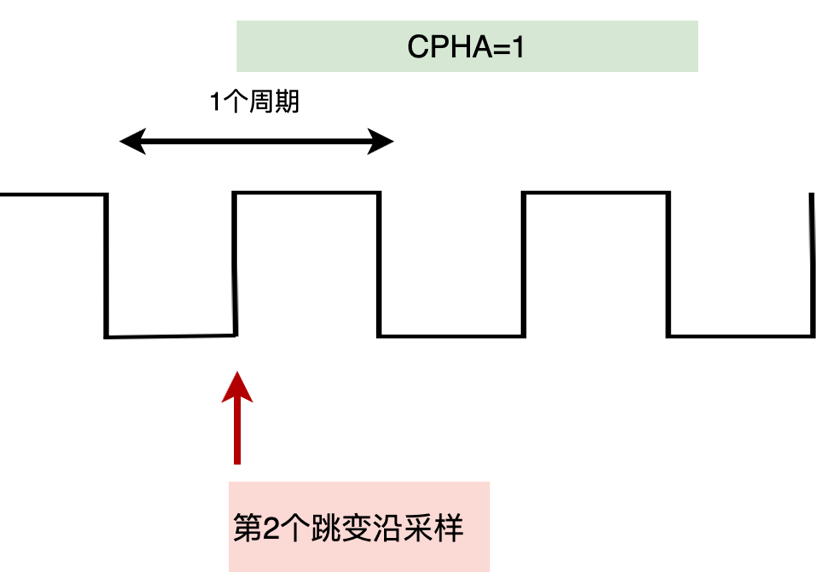

CPHA:clock phase,就是时钟相位。

直接决定SPI总线从哪个跳变沿开始采样数据。

CPHA=0:表示从第一个跳变沿开始采样;

CPHA=1:表示从第二个跳变沿开始采样。

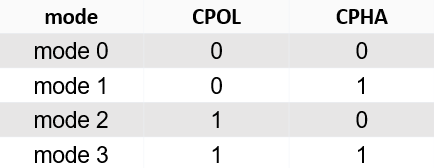

SPI的4种模式

时钟的2种极性和2种相位的不同组合,得到了SPI的4种工作模式。

模式0和模式2

模式1和模式3

不同点:空闲时刻处于高/低电平,第一次采集在第一次的跳变点/第二次跳变点。

很多设备支持模式0和模式3。

我们大多选择模式0。