GPIO概述

GPIO(General-purpose input/output),通用型输入输出。简单理解就是我们可以控制输入输出的STM32引脚,统称为GPIO。

GPIO存在的意义就是用程序控制或读取它们的输出或输入。

GPIO总体说明

STM32有多组GPIO,比如我们使用的芯片:STM32F103ZET6共有7组GPIO端口,他们分别是GPIOx(x从A-G),每组控制16个引脚,共有112个GPIO引脚。具体一个其他STM32芯片有多少组GPIO,可以去查看他们的对应的数据手册。

每个引脚的电平是0-3.3V,部分引脚最高可以兼容到5V。

GPIO的主要特点

不同型号,IO口的数量可能不一样。

快速翻转。最快可以达到每2个时钟周期翻转一次。(STM32F1系列最快可以达到50MHz的翻转速度)。

每个IO都可以作为外部中断。

支持8种工作模式。

GPIO的8种工作模式

GPIO端口的每个位(引脚)可以由软件分别配置成8种模式,当然对同一个引脚同一时间只能处于某一种模式中。

输入浮空(Input floating)

输入上拉(Input pull-up)

输入下拉(Input-pull-down)

模拟输入(Analog)

通用开漏输出(Output open-drain)

通用推挽式输出(Output push-pull)

推挽式复用功能(Alternate function push-pull)

开漏复用功能(Alternate function open-drain)

每个I/O端口位可以自由编程,然而I/O端口寄存器必须按32位字被访问。

输出模式下可以控制端口输出高电平低电平,用于驱动LED,蜂鸣器等,如果是大功率器件(比如电机),还需要加上驱动器(小电流控制大电流)。

输入模式下可以读取端口的高低电平,用于读取外接按键,外接模拟信号的输入,ADC电压采集,模拟通信协议接受数据等。

GPIO工作模式

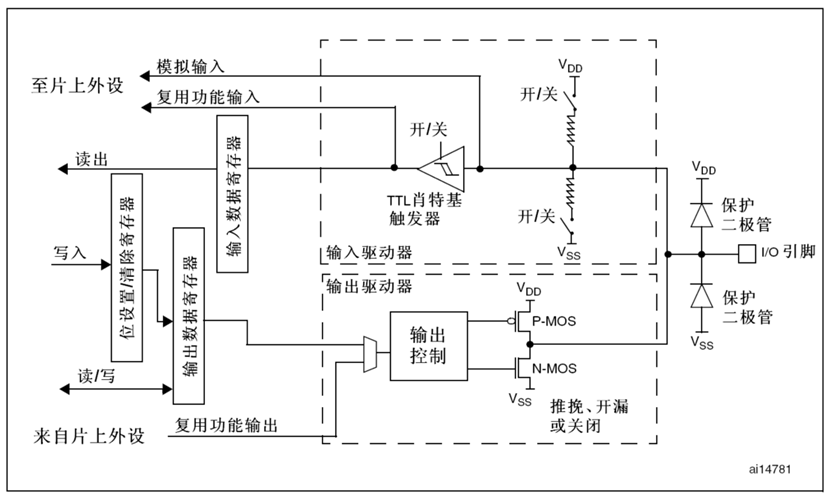

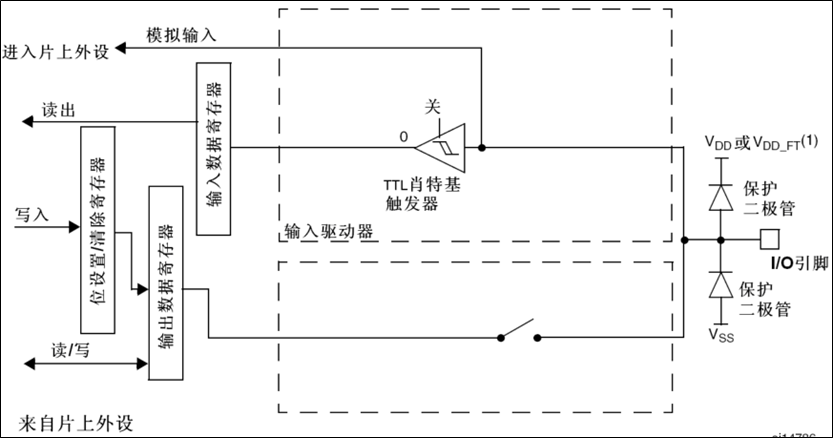

GPIO每位的具体电路结构

输出模式

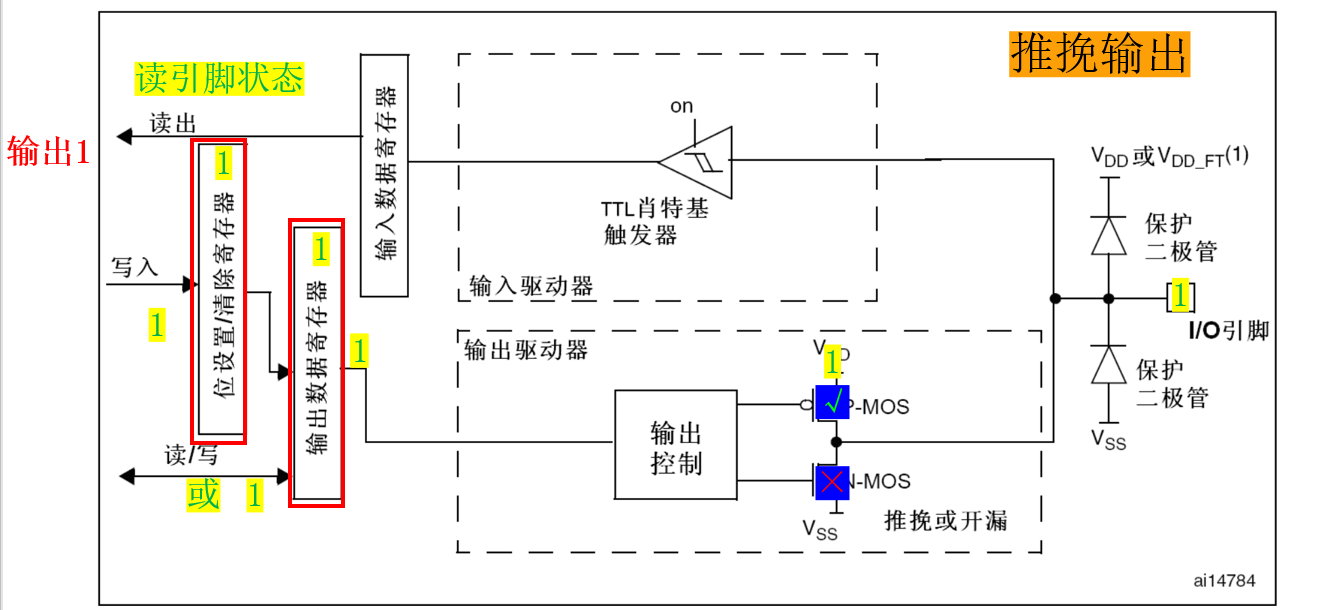

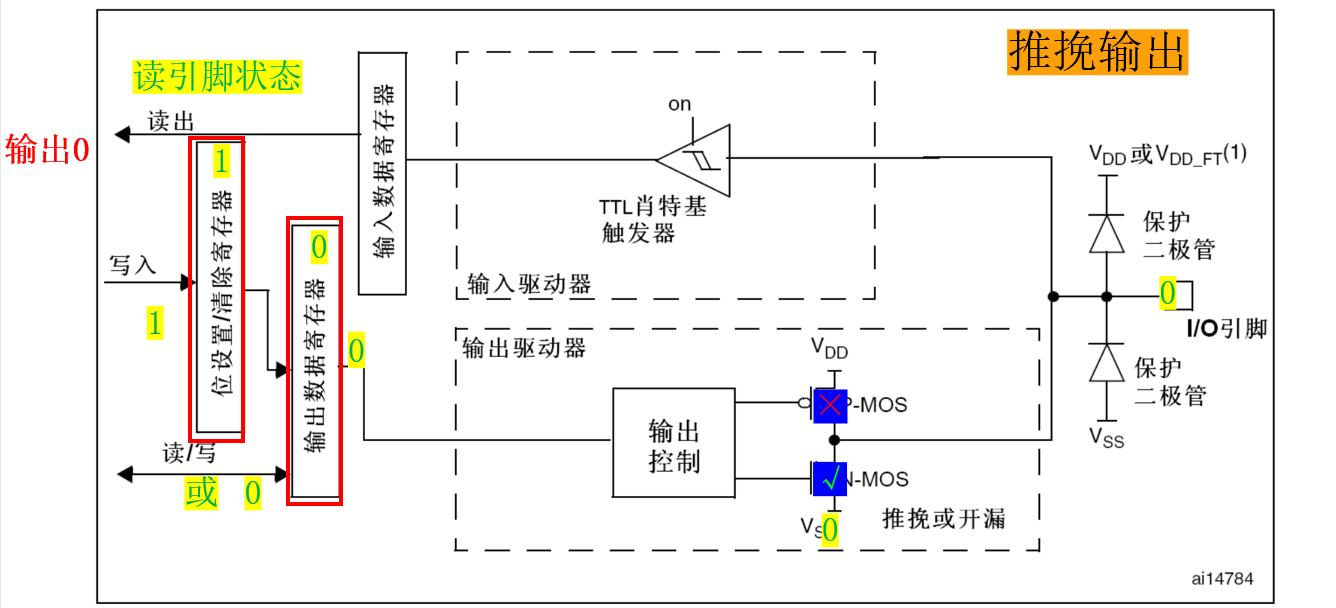

推挽输出

向设置/清除寄存器对应的设置位或清除位写1;或者直接输出寄存器的对应位写1或0,即可完成想要的输出。

可以从输入寄存器读取引脚状态。

工作时两个MOS管交替工作来驱动负载。

输出1时,上部晶体管导通将电流推向负载;

输出0时,下部晶体管导通,将电流拉回地线。

所以叫推挽输出。

在推挽模式时,对输出数据寄存器的读访问得到最后一次写的值。

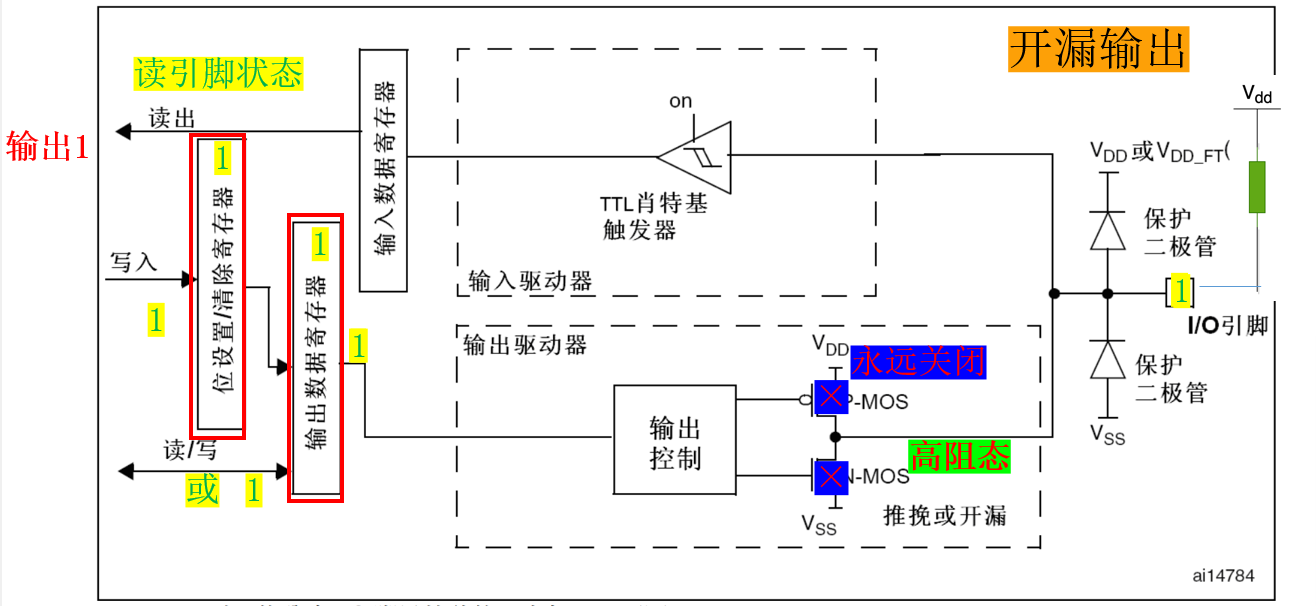

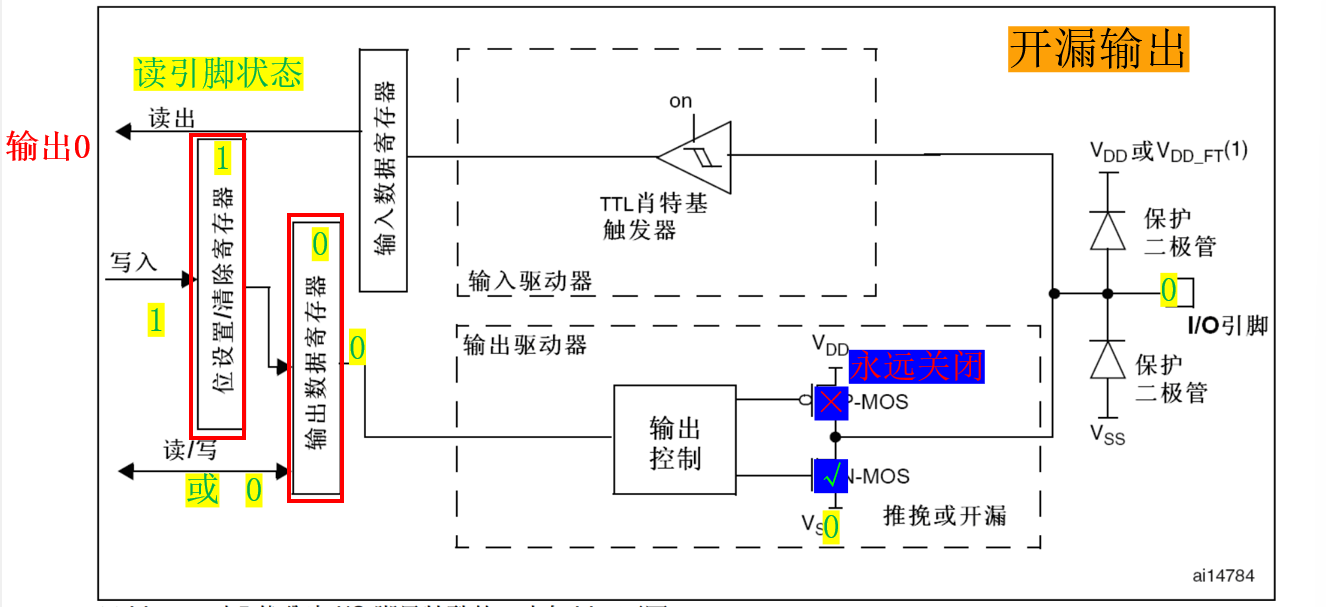

开漏输出

上部晶体管永远关闭。

因此可以输出0,但是要输出1的话必须接上拉电阻。

在开漏模式时,对输入数据寄存器的读访问可得到I/O状态。

推挽输出和开漏输出的选择

使用推挽

驱动能力需求较高的场合。

高速信号传输。

无需公共信号线的场合。

使用开漏

多个设备共用信号线。

不同电压系统之间的接口。

需要外部上拉电阻来确定逻辑高电平的场合。

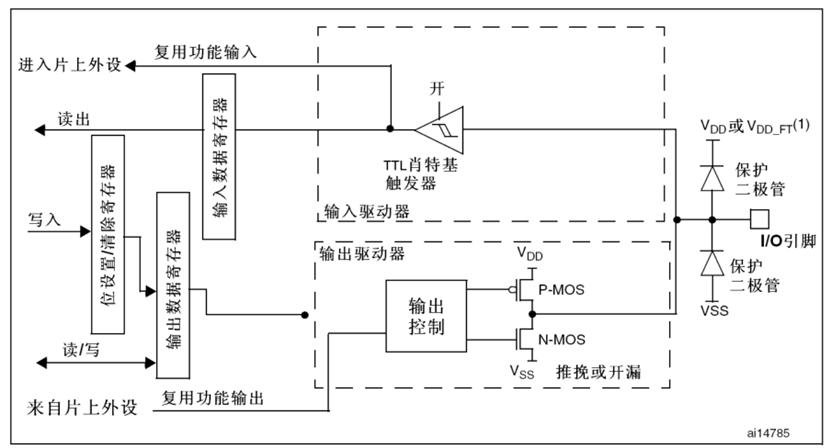

复用输出模式

在开漏或推挽配置中,输出缓冲器被打开。

内置外设的信号驱动输入缓冲器(复用功能输出)。

施密特触发输入被激活。

弱上拉和下拉电阻被禁止。

在每一个APB2时钟周期,出现在I/O脚上的数据被采样到输入数据寄存器。

开漏模式时,读输入数据寄存器时,可得到I/O口状态。

推完模式时,读输出数据寄存器时,可得到最后一次写的值。

输入模式

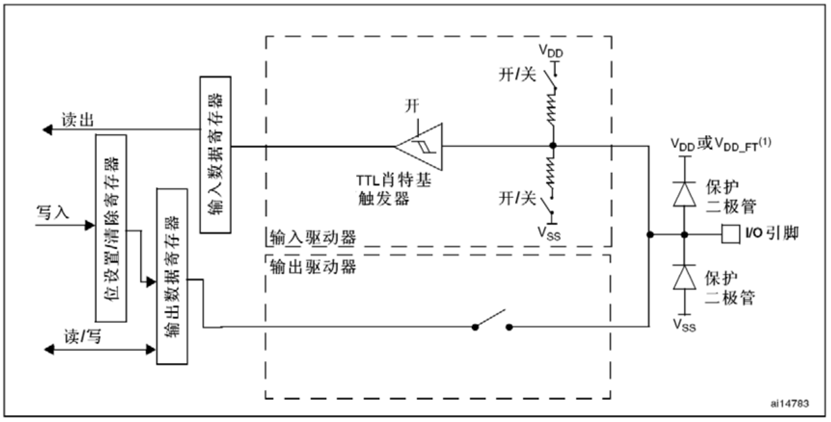

(1)2个保护二极管的作用是保护我们的芯片不会由于电压过高或过低而烧毁。

VDD接电源,VSS接地。

如果IO引脚的输入电压高于VDD的值到一定程度,上方保护二极管导通,则引脚电压被拉底到VDD。

如果IO引脚的输入电压低于VSS到一定程度,则下方保护二极管导通,电压被拉高到VSS。

(2)2个开关控制引脚在没有输入的时候上拉,下拉还是浮空。

当上面的开关闭合的时候,输入被拉高到高电平。

当下面的开关闭合的时候,输入被拉底到低电平。

如果两个都不闭合,输入就是悬空状态。

如果两个同时闭合,就是费电了,不会这么做。

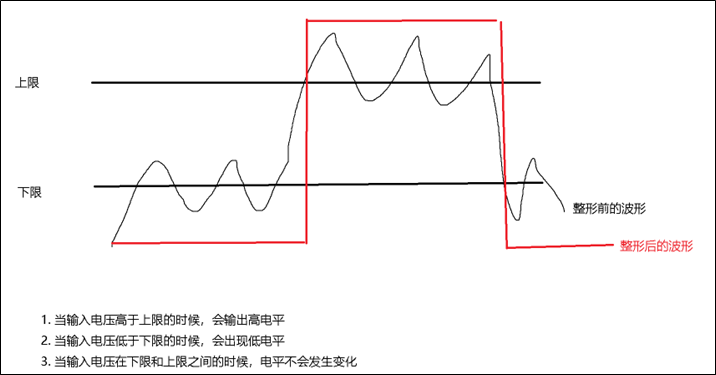

(3)施密特触发器(图中的TTL肖特基触发器)是包含正反馈的比较器电路。可以对信号进行波形整形。

(4)从施密特触发器出来的数据,进入到数据寄存器中,我们就可以从中读取数据了。

模拟输入模式

当配置为模拟输入的时候:

输出部分被禁止。

禁止施密特触发输入,实现了每个I/O引脚上的零消耗。施密特触发出值被强制置为0。

弱上拉和下拉电阻被禁止。

读取输入数据寄存器的值永远为0。

与GPIO相关的7个寄存器

每个GPIO端口有7个相关的寄存器:

2个32位配置寄存器(GPIOx_CRL,GPIOx_CRH)。

2个32位数据寄存器(GPIOx_IDR和GPIOx_ODR)。

1个32位置位/复位寄存器(GPIOx_BSRR)。

1个16位复位寄存器(GPIOx_BRR)。

1个32位锁定寄存器(GPIOx_LCKR)。

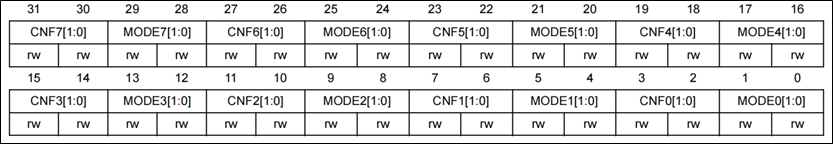

GPIOx_CRL(端口配置低寄存器)

GPIOx_CRL(Port configuration register low),x可以是A-G。

该寄存器配置的每个GPIO的 0-7 这个8个位,所以叫低寄存器。

MODE:每个端口有2个MODE位进行控制。

00:输入模式(复位后的状态)

01:输出模式,最大速度10MHz

10:输出模式,最大速度2MHz

11:输出模式,最大速度50MHz

CNF:每个端口有2个CNF位进行控制。

当MODE是00(输入模式):

00:模拟输入模式

01:浮空输入模式(复位后的状态)

10:上拉/下拉输入模式

11:保留

当MODE>00(输出模式)

00:通用推挽输出模式

01:通用开漏输出模式

10:复用功能推挽输出模式

11:复用功能开漏输出模式

GPIOx_CRH(端口配置高寄存器)

GPIOx_CRH(Port configuration register high)。

该寄存器配置的是每个端口的 8-15引脚,配置方式和低位寄存器完全一样。

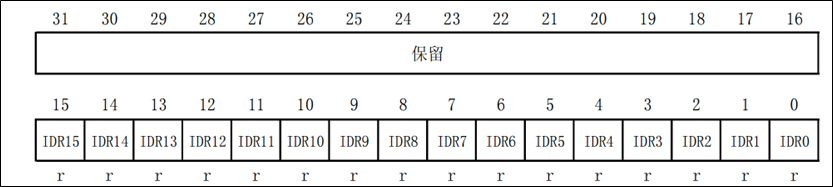

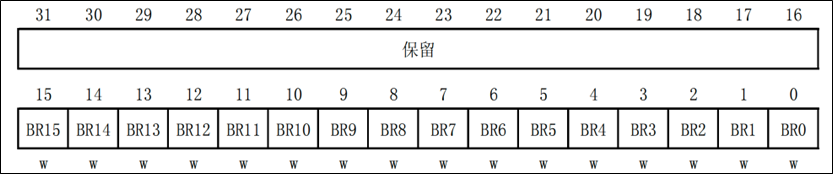

GPIOx_IDR(端口输入数据寄存器)

Port input data register

保留位始终读为0。剩下的分别对应每个引脚的输入值。

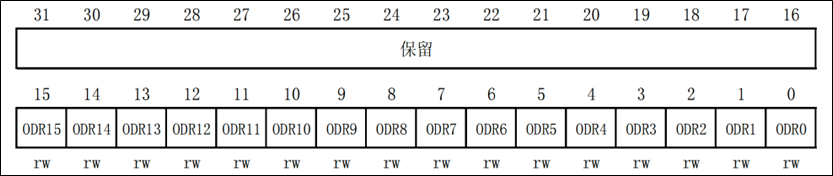

GPIOx_ODR(端口输出数据寄存器)

Port output data register

保留位始终读为0。剩下的分别对应每个引脚的输出值。

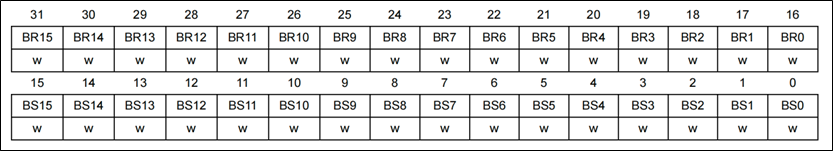

GPIOx_BSRR(端口位设置/清除寄存器)

Port bit set/reset register

高16位是用清除对应的数据输出寄存器的位(0-15)的值:设置为0不影响,设置为1会清除ODR对应的位的值(置为0)。

低16位是用设置对应的数据输出寄存器的位(0-15)的值:设置为0不影响,设置为1会设置ODR对应的位的值(置为1)。

GPIOx_BRR(端口位清除寄存器)

这个寄存器具有了GPIOx_BSRR一半的功能:清除。

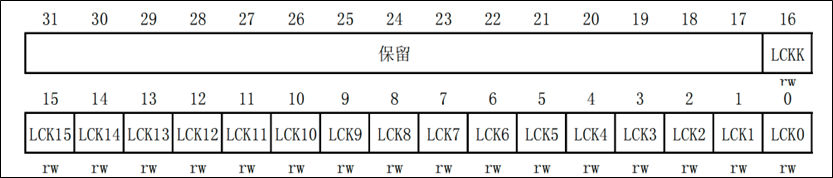

GPIOx_LCKR(端口配置锁定寄存器)

Port configuration lock register

该寄存器用来锁定端口位的配置。位[15:0]用于锁定GPIO端口的配置。在规定的写入操作期间,不能改变LCKR[15:0]。当对相应的端口位执行了LOCK序列后,在下次系统复位之前将不能再更改端口位的配置。

每个锁定位锁定控制寄存器(CRL,CRH)中相应的4个位(CNF2位和MODE2位)。

第16位用来激活锁定寄存器,必须按照规定的时序来操作才行: 写1 -> 写0 -> 写1 -> 读0 -> 读1。

对0-15位:

0:不锁定对应端口的配置。

1:锁定对应端口的配置。